- Manufacturer Part Number : AD6655ABCPZ-150

- Manufacturer : AD

- Description : IF Diversity Receiver IC

- Series : AD6655

- Reference Price : USD 81.304

- Our Price : We have a better price, contact us by email

- Product Type : Integrated/Special Purpose A/D Converters

- Function : IF/RF Receivers

- Current Suggest : Production

- Status : Production

- ROHS Status : ROHS Compliant (Lead Free)

- Package Type : 64-Lead LFCSP (9mm x 9mm w/ EP)

- Pins : 64

- MFG Package Case : CP-64-6

- Part Type : OTH

- Standard Packing Type : Tray

- Standard Packing Quantity : 260

- Working Temperature : -40 to 85C

- Other Part Number : AD6655ABCPZ-150

- Shipping methods : DHL FEDEX UPS TNT

- Delivery Time : Ship within 1 day.

- Manufacturer Production time : 6-8 weeks (Normally have stocks)

- Weight : 0.001KG

Contact us to check the best price and real time inventory quantity for AD6655ABCPZ-150. If you need any more information about AD6655ABCPZ-150, you can also send us by email. Our email is [email protected], we will reply you in 12 hours.

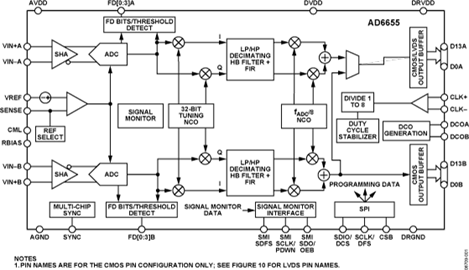

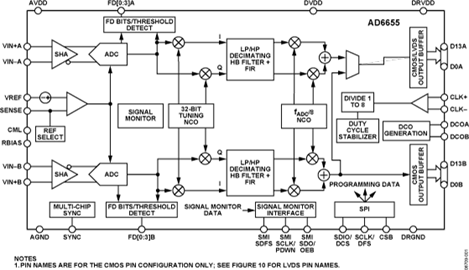

The AD6655 is a mixed-signal intermediate frequency (IF) receiver consisting of dual 14-bit, 80 MSPS/105 MSPS/125 MSPS/150 MSPS ADCs and a wideband digital downconverter (DDC). The AD6655 is designed to support communications applications where low cost, small size, and versatility are desired.

The dual ADC core features a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth differential sample-and-hold analog input amplifiers supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations. A duty cycle stabilizer is provided to compensate for variations in the ADC clock duty cycle, allowing the converters to maintain excellent performance.

ADC data outputs are internally connected directly to the digital downconverter (DDC) of the receiver, simplifying layout and reducing interconnection parasitics. The digital receiver has two channels and provides processing flexibility. Each receive channel has four cascaded signal processing stages: a 32-bit frequency translator (numerically controlled oscillator (NCO)), a half-band decimating filter, a fixed FIR filter, and an fADC/8 fixed-frequency NCO.

In addition to the receiver DDC, the AD6655 has several functions that simplify the automatic gain control (AGC) function in the system receiver. The fast detect feature allows fast overrange detection by outputting four bits of input level information with short latency.

In addition, the programmable threshold detector allows monitoring of the incoming signal power using the four fast detect bits of the ADC with low latency. If the input signal level exceeds the programmable threshold, the coarse upper threshold indicator goes high. Because this threshold indicator has low latency, the user can quickly turn down the system gain to avoid an overrange condition.

The second AGC-related function is the signal monitor. This block allows the user to monitor the composite magnitude of the incoming signal, which aids in setting the gain to optimize the dynamic range of the overall system.

After digital processing, data can be routed directly to the two external 14-bit output ports. These outputs can be set from 1.8 V to 3.3 V CMOS or as 1.8 V LVDS. The CMOS data can also be output in an interleaved configuration at a double data rate using only Port A.

The AD6655 receiver digitizes a wide spectrum of IF frequencies. Each receiver is designed for simultaneous reception of the main channel and the diversity channel. This IF sampling architecture greatly reduces component cost and complexity compared with traditional analog techniques or less integrated digital methods.

Flexible power-down options allow significant power savings, when desired.

Programming for setup and control is accomplished using a 3-bit SPI-compatible serial interface.

The AD6655 is available in a 64-lead LFCSP and is specified over the industrial temperature range of −40°C to +85°C.

Product Highlights

- Integrated dual, 14-bit, 150 MSPS ADC.

- Integrated wideband decimation filter and 32-bit complex NCO.

- Fast overrange detect and signal monitor with serial output.

- Proprietary differential input maintains excellent SNR performance for input frequencies up to 450 MHz.

- Flexible output modes, including independent CMOS, interleaved CMOS, IQ mode CMOS, and interleaved LVDS.

- SYNC input allows synchronization of multiple devices.

- 3-bit SPI port for register programming and register readback.

- Communications

- Diversity radio systems

- Multimode digital receivers (3G)

- TD-SCDMA, WiMax, WCDMA, CDMA2000, GSM, EDGE, LTE

- I/Q demodulation systems

- Smart antenna systems

- General-purpose software radios

- Broadband data applications

At least one model within this product family is in production and available for purchase. The product is appropriate for new designs but newer alternatives may exist.