- Manufacturer Part Number : AD6674-LF1000EBZ

- Manufacturer : AD

- Description : 385 MHz BW IF Diversity Receiver IC

- Series : AD6674

- Reference Price : USD 0

- Our Price : We have a better price, contact us by email

- Product Type : Integrated/Special Purpose A/D Converters

- Function : IF/RF Receivers

- Current Suggest : Recommended for New Designs

- Status : Production

- ROHS Status : ROHS Compliant (Lead Free)

- Package Type : Evaluation board for AD6674-1000 (Up to 1GHz Input Bandwidth)

- Pins : -

- MFG Package Case : -

- Part Type : EVAL

- Standard Packing Type : -

- Standard Packing Quantity : -

- Working Temperature : -

- Other Part Number : AD6674-LF1000EBZ

- Shipping methods : DHL FEDEX UPS TNT

- Delivery Time : Ship within 1 day.

- Manufacturer Production time : 6-8 weeks (Normally have stocks)

- Weight : 0.001KG

Contact us to check the best price and real time inventory quantity for AD6674-LF1000EBZ. If you need any more information about AD6674-LF1000EBZ, you can also send us by email. Our email is [email protected], we will reply you in 12 hours.

- JESD204B (Subclass 1) coded serial digital outputs

- In band SFDR = 83 dBFS at 340 MHz (750 MSPS)

- In band SNR = 66.7 dBFS at 340 MHz (750 MSPS)

- 1.4 W total power per channel at 750 MSPS (default settings)

- Noise density = −153 dBFS/Hz at 750 MSPS

- 1.25 V, 2.5 V, and 3.3 V dc supply operation

- Flexible input range

- AD6674-750 and AD6674-1000

- 1.46 V p-p to 1.94 V p-p (1.70 V p-p nominal)

- AD6674-500

- 1.46 V p-p to 2.06 V p-p (2.06 V p-p nominal)

- AD6674-750 and AD6674-1000

- 95 dB channel isolation/crosstalk

- Amplitude detect bits for efficient automatic gain control (AGC) implementation

- Noise shaping requantizer (NSR) option for main receiver function

- Variable dynamic range (VDR) option for digital predistortion (DPD) function

- 2 integrated wideband digital processors per channel

- 12-bit numerically controlled oscillator (NCO), up to 4 cascaded half-band filters

- Differential clock inputs

- Integer clock divide by 1, 2, 4, or 8

- Energy saving power-down modes

- Flexible JESD204B lane configurations

- Small signal dither

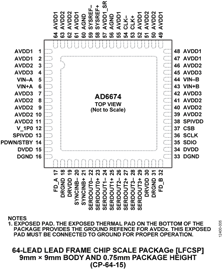

The AD6674 is a 385 MHz bandwidth mixed-signal intermediate frequency (IF) receiver. It consists of two, 14-bit 1.0 GSPS/750 MSPS/500 MSPS analog-to-digital converters (ADC) and various digital signal processing blocks consisting of four wideband DDCs, an NSR, and VDR monitoring. It has an on-chip buffer and a sample-and-hold circuit designed for low power, small size, and ease of use. This product is designed to support communications applications capable of sampling wide bandwidth analog signals of up to 2 GHz. The AD6674 is optimized for wide input bandwidth, high sampling rate, excellent linearity, and low power in a small package.

The dual ADC cores feature a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations.

Applications

- Diversity multiband, multimode digital receivers 3G/4G, TD-SCDMA, W-CDMA, GSM, LTE, LTE-A

- DOCSIS 3.0 CMTS upstream receive paths

- HFC digital reverse path receivers

This product has been released to the market. The data sheet contains all final specifications and operating conditions. For new designs, ADI recommends utilization of these products.