- Manufacturer Part Number : AD9695

- Manufacturer : AD

- Description : 14-Bit, 1300 MSPS/625 MSPS, JESD204B, Dual Analog-to-Digital Converter

- Series : AD9695

- Reference Price : USD 608.6

- Our Price : We have a better price, contact us by email

- Product Type : High Speed A/D Converters >10 MSPS

- Function : Standard High Speed A/D Converters >20 MSPS

- Current Suggest : Recommended for New Designs

- Status : Production

- RoHS Status: -

- Voltage: -

- Feature: -

- Package Case: -

- Temperature Range: -

- Packing: Reel/Tray/Tube

- Standard Packing Quantity: -

- Country of Origin: -

- Other Part Number : AD9695

- Shipping methods : DHL FEDEX UPS TNT

- Delivery Time : Ship within 1 day.

- Manufacturer Production time : 6-8 weeks (Normally have stocks)

- Weight : 0.001KG

Contact us to check the best price and real time inventory quantity for AD9695. If you need any more information about AD9695, you can also send us by email. Our email is [email protected], we will reply you in 12 hours.

- JESD204B (Subclass 1) coded serial digital outputs

- Lane rates up to 16 Gbps

- 1.6 W total power at 1300 MSPS

- 800 mW per ADC channel

- SNR = 65.6 dBFS at 172 MHz (1.59 V p-p input range)

- SFDR = 78 dBFS at 172.3 MHz (1.59 V p-p input range)

- Noise density

- −153.9 dBFS/Hz (1.59 V p-p input range)

- −155.6 dBFS/Hz (2.04 V p-p input range)

- 0.95 V, 1.8 V, and 2.5 V supply operation

- No missing codes

- Internal ADC voltage reference

- Flexible input range

- 1.36 V p-p to 2.04 V p-p (1.59 V p-p typical)

- 2 GHz usable analog input full power bandwidth

- >95 dB channel isolation/crosstalk

- Amplitude detect bits for efficient AGC implementation

- 2 integrated digital downconverters per ADC channel

- 48-bit NCO

- Programmable decimation rates

- Differential clock input

- SPI control

- Integer clock divide by 2 and divide by 4

- Flexible JESD204B lane configurations

- On-chip dithering to improve small signal linearity

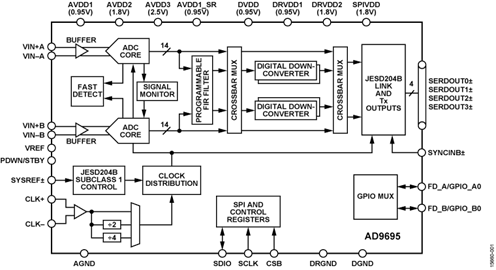

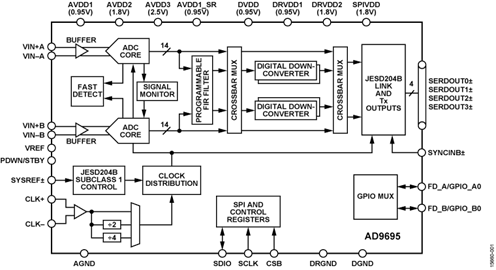

The AD9695 is a dual, 14-bit, 1300 MSPS/625 MSPS analog-to-digitalconverter (ADC). The device has an on-chip buffer and asample-and-hold circuit designed for low power, small size, andease of use. This product is designed to support communicationsapplications capable of direct sampling wide bandwidth analogsignals of up to 2 GHz. The −3 dB bandwidth of the ADC inputis 2 GHz. The AD9695 is optimized for wide input bandwidth,high sampling rate, excellent linearity, and low power in a smallpackage.

The dual ADC cores feature a multistage, differential pipelinedarchitecture with integrated output error correction logic. EachADC features wide bandwidth inputs supporting a variety ofuser-selectable input ranges. An integrated voltage referenceeases design considerations. The analog input and clock signalsare differential inputs. The ADC data outputs are internallyconnected to four digital downconverters (DDCs) through acrossbar mux. Each DDC consists of multiple signal processingstages: a 48-bit frequency translator (numerically controlledoscillator (NCO)), and decimation filters. The NCO has the optionto select up to 16 preset bands over the general-purpose input/output (GPIO) pins, or use a coherent fast frequency hoppingmechanism for band selection. Operation of the AD9695 betweenthe DDC modes is selectable via SPI-programmable profiles.

In addition to the DDC blocks, the AD9695 has several functionsthat simplify the automatic gain control (AGC) function in acommunications receiver. The programmable threshold detectorallows monitoring of the incoming signal power using the fastdetect control bits in Register 0x0245 of the ADC. If the inputsignal level exceeds the programmable threshold, the fast detectindicator goes high. Because this threshold indicator has lowlatency, the user can quickly turn down the system gain to avoidan overrange condition at the ADC input. In addition to the fastdetect outputs, the AD9695 also offers signal monitoringcapability. The signal monitoring block provides additionalinformation about the signal being digitized by the ADC.

The user can configure the Subclasss 1 JESD204B-based highspeed serialized output using either one lane, two lanes, or fourlanes, depending on the DDC configuration and the acceptablelane rate of the receiving logic device. Multidevice synchronizationis supported through the SYSREF± and SYNCINB± input pins.

The AD9695 has flexible power-down options that allowsignificant power savings when desired. All of these features canbe programmed using a 3-wire serial port interface (SPI) and orPDWN/STBY pin.

The AD9695 is available in a Pb-free, 64-lead LFCSP and isspecified over the −40°C to +105°C junction temperature range.This product may be protected by one or more U.S. orinternational patents.

Note that, throughout this data sheet, multifunction pins, suchas FD_A/GPIO_A0, are referred to either by the entire pinname or by a single function of the pin, for example, FD_A,when only that function is relevant.

Product Highlights

- Low power consumption per channel.

- JESD204B lane rate support up to 16 Gbps.

- Wide, full power bandwidth supports intermediate frequency (IF) sampling of signals up to 2 GHz.

- Buffered inputs ease filter design and implementation.

- Four integrated wideband decimation filters and NCO blocks supporting multiband receivers.

- Programmable fast overrange detection.

- On-chip temperature diode for system thermal management.

Applications

- Communications

- Diversity multiband, multimode digital receivers

- 3G/4G, TD-SCDMA, WCDMA, GSM, LTE

- General-purpose software radios

- Ultrawideband satellite receiver

- Instrumentation

- Oscilloscopes

- Spectrum analyzers

- Network analyzers

- Integrated RF test solutions

- Radars

- Electronic support measures, electronic counter measures, and electronic counter-counter measures

- High speed data acquisition systems

- DOCSIS 3.0 CMTS upstream receive paths

- Hybrid fiber coaxial digital reverse path receivers

- Wideband digital predistortion

This product has been released to the market. The data sheet contains all final specifications and operating conditions. For new designs, ADI recommends utilization of these products.