- Manufacturer Part Number : AD9554BCPZ

- Manufacturer : AD

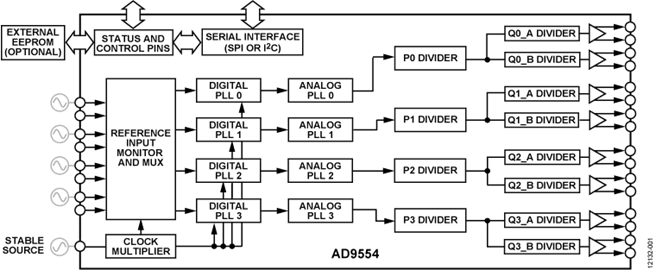

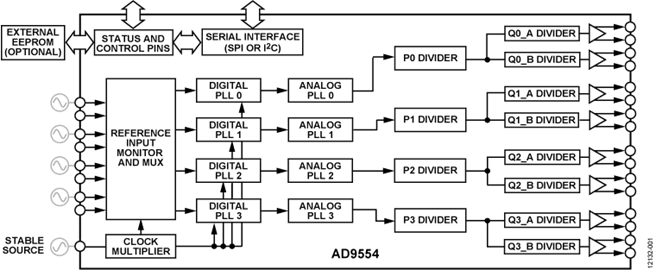

- Description : Quad PLL, Quad Input, 8-output Multiservice Line Card Adaptive Clock Translator IC

- Series : AD9554

- Reference Price : USD 17.064

- Our Price : We have a better price, contact us by email

- Product Type : Clock Generation & Distribution

- Function : Clock Synchronization

- Current Suggest : Recommended for New Designs

- Status : Production

- ROHS Status : ROHS Compliant (Lead Free)

- Package Type : 72-Lead LFCSP (10mm x 10mm w/ EP)

- Pins : 72

- MFG Package Case : CP-72-4

- Part Type : OTH

- Standard Packing Type : Tray

- Standard Packing Quantity : 168

- Working Temperature : -40 to 85C

- Other Part Number : AD9554BCPZ

- Shipping methods : DHL FEDEX UPS TNT

- Delivery Time : Ship within 1 day.

- Manufacturer Production time : 6-8 weeks (Normally have stocks)

- Weight : 0.001KG

Contact us to check the best price and real time inventory quantity for AD9554BCPZ. If you need any more information about AD9554BCPZ, you can also send us by email. Our email is [email protected], we will reply you in 12 hours.

The AD9554 is a low loop bandwidth clock translator that provides jitter cleanup and synchronization for many systems, including synchronous optical networks (SONET/SDH). The AD9554 generates an output clock synchronized to up to four external input references. The digital PLL (DPLL) allows for reduction of input time jitter or phase noise associated with the external references. The digitally controlled loop and holdover circuitry of the AD9554 continuously generates a low jitteroutput clock even when all reference inputs have failed.

The AD9554 operates over an industrial temperature range of −40°C to +85°C. If a smaller device is needed, the AD9554-1 is a version of this device with one output per PLL. If a single or dual DPLL version of this device is needed, refer to the AD9557 or AD9559, respectively.

Applications

- Network synchronization, including synchronous Ethernet and synchronous digital hierarchy (SDH) to optical transport network (OTN) mapping/demapping

- Cleanup of reference clock jitter

- SONET/SDH clocks up to OC-192, including FEC

- Stratum 3 holdover, jitter cleanup, and phase transient control

- Cable infrastructure

- Data communications

- Professional video

This product has been released to the market. The data sheet contains all final specifications and operating conditions. For new designs, ADI recommends utilization of these products.