- Manufacturer Part Number : AD9574

- Manufacturer : AD

- Description : Ethernet/Gigabit Ethernet Clock Generator

- Series : AD9574

- Reference Price : USD 2.448

- Our Price : We have a better price, contact us by email

- Product Type : Clock Generation & Distribution

- Function : Clock Generation Devices

- Current Suggest : Recommended for New Designs

- Status : Production

- RoHS Status: -

- Voltage: -

- Feature: -

- Package Case: -

- Temperature Range: -

- Packing: Reel/Tray/Tube

- Standard Packing Quantity: -

- Country of Origin: -

- Other Part Number : AD9574

- Shipping methods : DHL FEDEX UPS TNT

- Delivery Time : Ship within 1 day.

- Manufacturer Production time : 6-8 weeks (Normally have stocks)

- Weight : 0.001KG

Contact us to check the best price and real time inventory quantity for AD9574. If you need any more information about AD9574, you can also send us by email. Our email is [email protected], we will reply you in 12 hours.

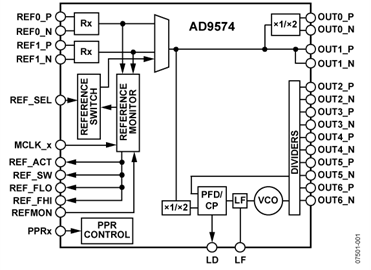

The AD9574 provides a multiple output clock generator function comprising a dedicated phase-locked loop (PLL) core optimized for Ethernet and gigabit Ethernet line card applications. The integer-N PLL design is based on the Analog Devices, Inc., proven portfolio of high performance, low jitter frequency synthesizers to maximize network performance. The AD9574 also benefits other applications requiring low phase noise and jitter performance.

Configuring the AD9574 for a particular application requires only the connection of external pull-up or pull-down resistors to the appropriate pin program reader pins (PPRx). These pins provide control of the internal dividers for establishing the desired frequency translations, clock output functionality, and input reference functionality. Connecting an external 19.44 MHz or 25 MHz oscillator to one or both of the REF0_P/REF0_N or REF1_P/REF1_N reference inputs results in a set of output frequencies prescribed by the PPRx pins. Connecting a stable clock source (8 kHz/10 MHz/19.44 MHz/25 MHz/38.88 MHz) to the monitor clock input enables the optional monitor circuit providing quality of service (QoS) status for REF0 or REF1.

The PLL section consists of a low noise phase frequency detector (PFD), a precision charge pump (CP), a partially integrated loop filter (LF), a low phase noise voltage controlled oscillator (VCO), and feedback and output dividers. The divider values depend on the PPRx pins. The integrated loop filter requires only a single external capacitor connected to the LF pin.

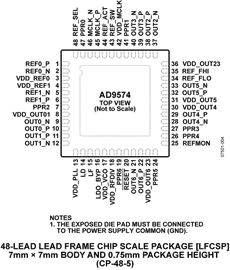

The AD9574 is packaged in a 48-lead 7 mm × 7 mm LFCSP, requiring only a single 3.3 V supply. The operating temperature range is −40°C to +85°C.

Applications

- Ethernet line cards, switches, and routers

- SATA and PCI express

- Low jitter, low phase noise clock generation

This product has been released to the market. The data sheet contains all final specifications and operating conditions. For new designs, ADI recommends utilization of these products.