- Manufacturer Part Number : AD9577

- Manufacturer : AD

- Description : Clock Generator with Dual PLLs, Spread Spectrum, and Margining

- Series : AD9577

- Reference Price : USD 3.472

- Our Price : We have a better price, contact us by email

- Product Type : Clock Generation & Distribution

- Function : Clock Generation Devices

- Current Suggest : Recommended for New Designs

- Status : Production

- RoHS Status: -

- Voltage: -

- Feature: -

- Package Case: -

- Temperature Range: -

- Packing: Reel/Tray/Tube

- Standard Packing Quantity: -

- Country of Origin: -

- Other Part Number : AD9577

- Shipping methods : DHL FEDEX UPS TNT

- Delivery Time : Ship within 1 day.

- Manufacturer Production time : 6-8 weeks (Normally have stocks)

- Weight : 0.001KG

Contact us to check the best price and real time inventory quantity for AD9577. If you need any more information about AD9577, you can also send us by email. Our email is [email protected], we will reply you in 12 hours.

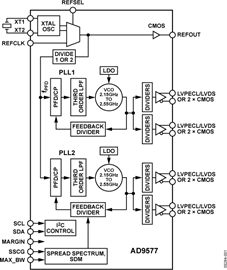

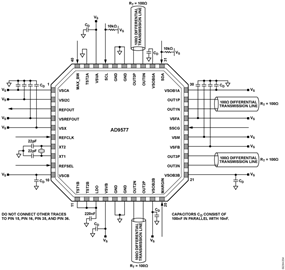

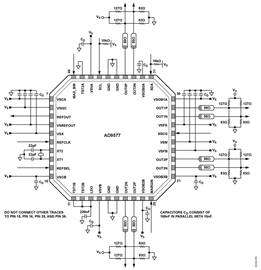

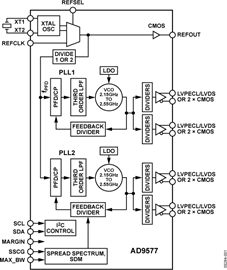

The AD9577 provides a multioutput clock generator function,along with two on-chip phase-locked loop cores, PLL1 and PLL2,optimized for network clocking applications. The PLL designsare based on the Analog Devices, Inc., proven portfolio of highperformance, low jitter frequency synthesizers to maximizenetwork performance. The PLLs have I2C programmable outputfrequencies and formats. The fractional-N PLL can supportspread spectrum clocking for reduced EMI radiated peak power.Both PLLs can support frequency margining. Other applicationswith demanding phase noise and jitter requirements can benefitfrom this part.

The first integer-N PLL section (PLL1) consists of a low noise phasefrequency detector (PFD), a precision charge pump (CP), a lowphase noise voltage controlled oscillator (VCO), a programmablefeedback divider, and two independently programmable outputdividers. By connecting an external crystal or applying a referenceclock to the REFCLK pin, frequencies of up to 637.5 MHz canbe synchronized to the input reference. Each output divider andfeedback divider ratio is I2C programmed for the requiredoutput rates.

A second fractional-N PLL (PLL2) with a programmable modulusallows VCO frequencies that are fractional multiples of thereference frequency to be synthesized. Each output dividerand feedback divider ratio can be programmed for the requiredoutput rates, up to 637.5 MHz. This fractional-N PLL can alsooperate in integer-N mode for the lowest jitter.

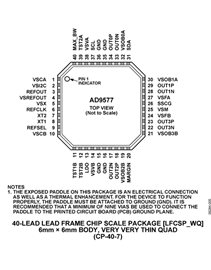

Up to four differential output clock signals can be configuredas either LVPECL or LVDS signaling formats. Alternatively,the outputs can be configured for up to eight CMOS outputs.Combinations of these formats are supported. No external loopfilter components are required, thus conserving valuable designtime and board space. The AD9577 is available in a 40-lead, 6 mm ×6 mm LFCSP package and can operate from a single 3.3 V supply.The operating temperature range is −40°C to +85°C.

Applications

- Low jitter, low phase noise multioutput clock generator for data communications applications including Ethernet, Fibre Channel, SONET, SDH, PCI-e, SATA, PTN, OTN, ADC/DAC, and digital video

- Spread spectrum clocking

This product has been released to the market. The data sheet contains all final specifications and operating conditions. For new designs, ADI recommends utilization of these products.