- Manufacturer Part Number : AD9578

- Manufacturer : AD

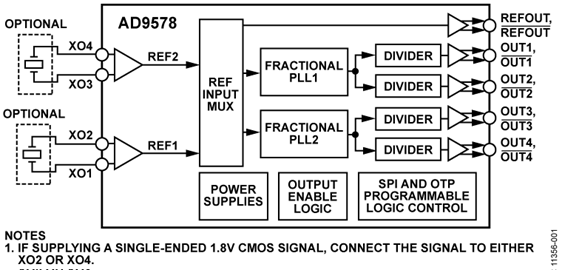

- Description : Dual PLL Precision Synthesizer

- Series : AD9578

- Reference Price : USD 6.032

- Our Price : We have a better price, contact us by email

- Product Type : Clock Generation & Distribution

- Function : Clock Generation Devices

- Current Suggest : Recommended for New Designs

- Status : Production

- RoHS Status: -

- Voltage: -

- Feature: -

- Package Case: -

- Temperature Range: -

- Packing: Reel/Tray/Tube

- Standard Packing Quantity: -

- Country of Origin: -

- Other Part Number : AD9578

- Shipping methods : DHL FEDEX UPS TNT

- Delivery Time : Ship within 1 day.

- Manufacturer Production time : 6-8 weeks (Normally have stocks)

- Weight : 0.001KG

Contact us to check the best price and real time inventory quantity for AD9578. If you need any more information about AD9578, you can also send us by email. Our email is [email protected], we will reply you in 12 hours.

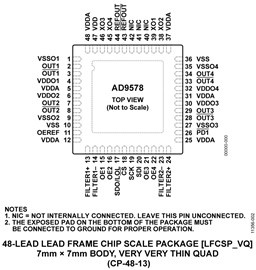

The AD9578 is a programmable synthesizer intended for jitter attenuation and asynchronous clocking applications in high performance telecommunications, networking, data storage, serializer/deserializer (SERDES), and physical layer (PHY) applications. The device incorporates two low jitter PLLs that provide any frequency with precision better than 0.1 ppb, each with two separate output dividers, for a total of four programmable outputs, delivering maximum flexibility and jitter performance. Each output is independently programmable to provide frequen-cies of up to 919 MHz with <410 fs typical rms jitter (12 kHz to 20 MHz) utilizing compact, low cost fundamental mode crystals (XTALs) that enable a robust supply chain. Using integer frequency synthesis, the AD9578 is capable of achieving rms jitter as low as 290 fs.

The AD9578 is packaged with a factory programmed default power-on configuration. After power-on, all settings including output frequency are reconfigurable through a fast SPI.

The AD9578 architecture permits it to be used as a numerically controlled oscillator (NCO). This allows the user to dynamically change the frequency using the fast SPI bus. FPGAs and other devices can take advantage of this function to implement digital PLLs with configurable loop bandwidths for jitter attenuation applications, precision disciplined clocks that lock to tight stability references, or digitally controlled precision timing applications, such as network timing and IEEE 1588 applications. The SPI bus can operate up to 50 MHz, enabling fast FPGA loops while multiple devices share the same bus. The AD9578 can also be used in multirate precision applications, such as broadcast video or OTN. HDL FPGA code for digital PLL applications is available from Analog Devices, Inc.

Applications

- FPGA-based jitter attenuators and low jitter PLLs

- Precision disciplined clocks and clock synthesizers

- Multirate clock synthesizers

- Optical: OTN/SDH/SONET

- Broadcast video: 3G SDI, HD SDI, SDI

- Networking and storage: Ethernet/SAS/Fibre Channel

- Wireless infrastructure: OBSAI/CPRI

- Industrial: IEEE 1588

- Numerically controlled oscillators (NCOs)

This product has been released to the market. The data sheet contains all final specifications and operating conditions. For new designs, ADI recommends utilization of these products.