- Manufacturer Part Number : AD-FMCDAQ2-EBZ

- Manufacturer : AD

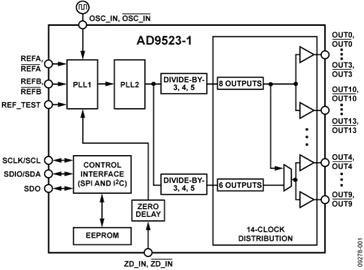

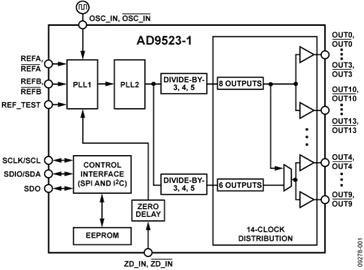

- Description : Low Jitter Clock Generator with 14 LVPECL/LVDS/HSTL/29 LVCMOS Outputs IC

- Series : AD9523-1

- Reference Price : USD 0

- Our Price : We have a better price, contact us by email

- Product Type : Clock Generation & Distribution

- Function : Clock Generation Devices

- Current Suggest : Recommended for New Designs

- Status : Production

- ROHS Status : ROHS Compliant (Lead Free)

- Package Type : AD-FMCDAQ2-EBZ Wideband RF data acquisition and signal synthesis module

- Pins : -

- MFG Package Case : -

- Part Type : EVAL

- Standard Packing Type : -

- Standard Packing Quantity : -

- Working Temperature : -

- Other Part Number : AD-FMCDAQ2-EBZ

- Shipping methods : DHL FEDEX UPS TNT

- Delivery Time : Ship within 1 day.

- Manufacturer Production time : 6-8 weeks (Normally have stocks)

- Weight : 0.001KG

Contact us to check the best price and real time inventory quantity for AD-FMCDAQ2-EBZ. If you need any more information about AD-FMCDAQ2-EBZ, you can also send us by email. Our email is [email protected], we will reply you in 12 hours.

- Output frequency: <1 MHz to 1 GHz

- Start-up frequency accuracy: <±100 ppm (determined by VCXO reference accuracy)

- Zero delay operation

Input-to-output edge timing: <150 ps - Dual VCO dividers

- 14 outputs: configurable LVPECL, LVDS, HSTL, and LVCMOS

- 14 dedicated output dividers with jitter-free adjustable delay

- Adjustable delay: 63 resolution steps of ½ period of VCO output divider

- Output-to-output skew: <50 ps

- Duty cycle correction for odd divider settings

- Automatic synchronization of all outputs on power-up

- Absolute output jitter: <150 fs at 122.88 MHz Integration range: 12 kHz to 20 MHz

- See data sheet for additional features

The AD9523-1 is designed to support the clock requirements for long term evolution (LTE) and multicarrier GSM base station designs. It relies on an external VCXO to provide the reference jitter cleanup to achieve the restrictive low phase noise requirements necessary for acceptable data converter SNR performance.

The input receivers, oscillator, and zero delay receiver provide both single-ended and differential operation. When connected to a recovered system reference clock and a VCXO, the device generates 14 low noise outputs with a range of 1 MHz to 1 GHz, and one dedicated buffered output from the input PLL (PLL1). The frequency and phase of one clock output relative to another clock output can be varied by means of a divider phase select function that serves as a jitter-free, coarse timing adjustment in increments that are equal to half the period of the signal coming out of the VCO.

An in-package EEPROM can be programmed through the serial interface to store user-defined register settings for power-up and chip reset.

Applications

- LTE and multicarrier GSM base stations

- Wireless and broadband infrastructure

- Medical instrumentation

- Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs

- Low jitter, low phase noise clock distribution

- Clock generation and translation for SONET, 10Ge, 10G FC, and other 10 Gbps protocols

- Forward error correction (G.710)

- High performance wireless transceivers

- ATE and high performance instrumentation

This product has been released to the market. The data sheet contains all final specifications and operating conditions. For new designs, ADI recommends utilization of these products.