- Manufacturer Part Number : EVAL-SDP-CS1Z

- Manufacturer : AD

- Description : Low Phase Noise, Fast Settling PLL Frequency Synthesizer IC

- Series : ADF4193

- Reference Price : USD 0

- Our Price : We have a better price, contact us by email

- Product Type : Phase Locked Loop (PLL) Synthesizers

- Function : Fractional-N PLL

- Current Suggest : Production

- Status : Production

- ROHS Status : ROHS Compliant (Lead Free)

- Package Type : SDP-S Controller Board - Interface to EV-ADF4193SD1Z and EV-ADF4193SD2Z (also required)

- Pins : -

- MFG Package Case : -

- Part Type : EVAL

- Standard Packing Type : -

- Standard Packing Quantity : -

- Working Temperature : -

- Other Part Number : EVAL-SDP-CS1Z

- Shipping methods : DHL FEDEX UPS TNT

- Delivery Time : Ship within 1 day.

- Manufacturer Production time : 6-8 weeks (Normally have stocks)

- Weight : 0.001KG

Contact us to check the best price and real time inventory quantity for EVAL-SDP-CS1Z. If you need any more information about EVAL-SDP-CS1Z, you can also send us by email. Our email is [email protected], we will reply you in 12 hours.

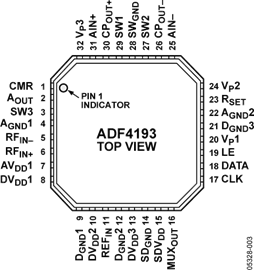

The ADF4193 frequency synthesizer can be used to implement local oscillators in the upconversion and downconversion sections of wireless receivers and transmitters. Its architecture is specifically designed to meet the GSM/EDGE lock time requirements for base stations. It consists of a low noise, digital phase frequency detector (PFD), and a precision differential charge pump. There is also a differential amplifier to convert the differential charge pump output to a single-ended voltage for the external voltage-controlled oscillator (VCO).

The Σ-Δ-based fractional interpolator, working with the N divider, allows programmable modulus fractional-N division. Additionally, the 4-bit reference (R) counter and on-chip frequency doubler allow selectable reference signal (REFIN) frequencies at the PFD input. A complete phase-locked loop (PLL) can be implemented if the synthesizer is used with an external loop filter and a VCO. The switching architecture ensures that the PLL settles inside the GSM time slot guard period, removing the need for a second PLL and associated isolation switches. This decreases cost, complexity, PCB area, shielding, and characterization on previous ping-pong GSM PLL architectures.

Applications

- GSM/EDGE base stations

- PHS base stations

- Instrumentation and test equipment

At least one model within this product family is in production and available for purchase. The product is appropriate for new designs but newer alternatives may exist.