- Manufacturer Part Number : HMC7043LP7FE

- Manufacturer : AD

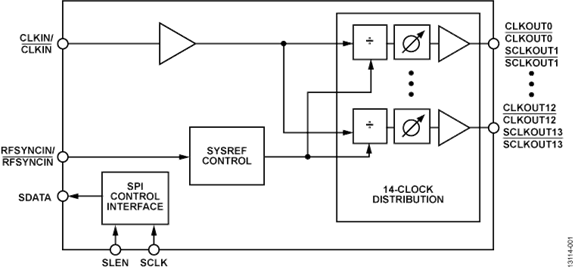

- Description : High Performance, 3.2 GHz, 14-Output Fanout Buffer with JESD204B/JESD204C IC

- Series : HMC7043

- Reference Price : USD 0

- Our Price : We have a better price, contact us by email

- Product Type : Clock Generation & Distribution

- Function : Clock Distribution Devices

- Current Suggest : Recommended for New Designs

- Status : Production

- ROHS Status : ROHS Compliant (Lead Free)

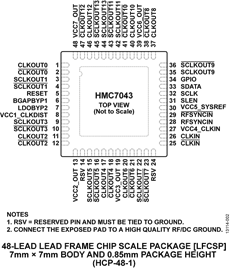

- Package Type : 48-Lead QFN (7mm x 7mm w/ EP)

- Pins : 48

- MFG Package Case : HCP-48-1

- Part Type : OTH

- Standard Packing Type : Cut Tape

- Standard Packing Quantity : 50

- Working Temperature : -40 to 85C

- Other Part Number : HMC7043LP7FE

- Shipping methods : DHL FEDEX UPS TNT

- Delivery Time : Ship within 1 day.

- Manufacturer Production time : 6-8 weeks (Normally have stocks)

- Weight : 0.001KG

Contact us to check the best price and real time inventory quantity for HMC7043LP7FE. If you need any more information about HMC7043LP7FE, you can also send us by email. Our email is [email protected], we will reply you in 12 hours.

The HMC7043 is designed to meet the requirements of multicarrier GSM and LTE base station designs, and offers a wide range of clock management and distribution features to simplify baseband and radio card clock tree designs.

The HMC7043 provides 14 low noise and configurable outputs to offer flexibility in interfacing with many different components in a base transceiver station (BTS) system, such as data converters, local oscillators, transmit/receive modules, field programmable gate arrays (FPGAs), and digital front-end ASICs. The HMC7043 can generate up to seven DCLK and SYSREF clock pairs per the JESD204B/JESD204C interface requirements.

The system designer can generate a lower number of DCLK and SYSREF pairs, and configure the remaining output signal paths for independent phase and frequency. Both the DCLK and SYSREF clock outputs can be configured to support different signaling standards, including CML, LVDS, LVPECL, and LVCMOS, and different bias conditions to adjust for varying board insertion losses.

One of the unique features of the HMC7043 is the independent flexible phase management of each of the 14 channels. All 14 channels feature both frequency and phase adjustment. The outputs can also be programmed for 50 Ω or 100 Ω internal and external termination options.

The HMC7043 device features an RF SYNC feature that synchronizes multiple HMC7043 devices deterministically, that is, ensures that all clock outputs start with the same edge. This operation is achieved by rephrasing the nested HMC7043 or SYSREF control unit/divider, deterministically, and then restarting the output dividers with this new phase.

The HMC7043 is offered in a 48-lead, 7 mm × 7 mm LFCSP package with an exposed pad connected to ground.

Applications

- JESD204B/JESD204C clock generation

- Cellular infrastructure (multicarrier GSM, LTE, W-CDMA)

- Data converter clocking

- Phase array reference distribution

- Microwave baseband cards

This product has been released to the market. The data sheet contains all final specifications and operating conditions. For new designs, ADI recommends utilization of these products.