- Manufacturer Part Number : HMC987LP5ETR

- Manufacturer : AD

- Description : 3.3V Low Noise 1:9 Fanout Buffer, DC - 8 GHz IC

- Series : HMC987

- Reference Price : USD 0

- Our Price : We have a better price, contact us by email

- Product Type : Clock Generation & Distribution

- Function : Clock Distribution Devices

- Current Suggest : Recommended for New Designs

- Status : Production

- ROHS Status : ROHS Compliant (Lead Free)

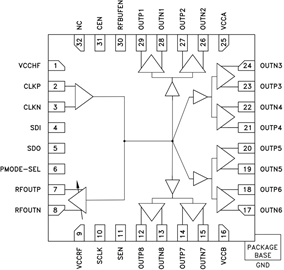

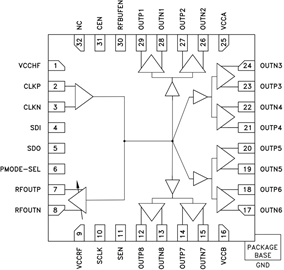

- Package Type : 32-Lead QFN (5mm x 5mm w/ EP)

- Pins : 32

- MFG Package Case : HCP-32-1

- Part Type : REEL

- Standard Packing Type : Reel

- Standard Packing Quantity : 500

- Working Temperature : -40 to 85C

- Other Part Number : HMC987LP5ETR

- Shipping methods : DHL FEDEX UPS TNT

- Delivery Time : Ship within 1 day.

- Manufacturer Production time : 6-8 weeks (Normally have stocks)

- Weight : 0.001KG

Contact us to check the best price and real time inventory quantity for HMC987LP5ETR. If you need any more information about HMC987LP5ETR, you can also send us by email. Our email is [email protected], we will reply you in 12 hours.

- Ultra Low Noise Floor: -166 dBc/Hz @ 2 GHz

- LVPECL, LVDS, CML & CMOS Compatible Inputs

- Up to 8 Differential or 16 Single-Ended LVPECL Outputs

- One Adjustable Power CML/RF Output

- Serial or Parallel Control, Hardware Chip-Enable

- Power-Down Current < 1 uA

- 32 Lead 5x5 mm SMT Package 25 mm²

The HMC987LP5E 1-to-9 fanout buffer is designed for low noise clock distribution. It is intended to generate relatively square wave outputs with rise/ fall times < 100 ps. The low skew and jitter outputs of the HMC987LP5E, combined with its fast rise/ fall times, leads to controllable low-noise switching of downstream circuits such as mixers, ADCs/DACs or SERDES devices. The noise floor is particularly important in these applications, when the clocknetwork bandwidth is wide enough to allow squarewave switching. Driven at 2 GHz, outputs of the HMC987LP5E have a noise floor of -166 dBc/Hz, corresponding to a jitter density of 0.6 asec/rtHz - or 50 fs over an 8 GHz bandwidth.

The input stage can be driven single-ended or differentially, in a variety of signal formats (CML, LVDS, LVPECL or CMOS), AC or DC coupled. The input stage also features adjustable input impedance. It has 8 LVPECL outputs, and 1 CML output with adjustable swing/power-level in 3 dB steps.

Individual output stages may be enabled or disabled for power-savings when not required using either hardware control pins, or under control of a serial-port interface.

Applications

- SONET, Fibre Channel, GigE Clock Distribution

- ADC/DAC Clock Distribution

- Low Skew and Jitter Clock or Data Fanout

- Wireless/Wired Communications

- Level Translation

- High Performance Instrumentation

- Medical Imaging

- Single-Ended to Differential Conversion

This product has been released to the market. The data sheet contains all final specifications and operating conditions. For new designs, ADI recommends utilization of these products.