- Manufacturer Part Number : ADRF6602ACPZ-R7

- Manufacturer : AD

- Description : 1000 MHz to 3100 MHz Rx Mixer with Integrated Fractional-N PLL and VCO IC

- Series : ADRF6602

- Reference Price : USD 0

- Our Price : We have a better price, contact us by email

- Product Type : RF Integrated Transmitters, Receivers, & Transceivers

- Function : RF Mixers with Integrated LO

- Current Suggest : Not Recommended for New Designs

- Status : Last Time Buy

- ROHS Status : ROHS Compliant (Lead Free)

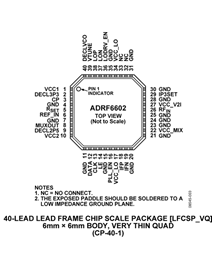

- Package Type : 40-Lead LFCSP (6mm x 6mm w/ EP)

- Pins : 40

- MFG Package Case : CP-40-1

- Part Type : REEL

- Standard Packing Type : Reel

- Standard Packing Quantity : 750

- Working Temperature : -40 to 85C

- Other Part Number : ADRF6602ACPZ-R7

- Shipping methods : DHL FEDEX UPS TNT

- Delivery Time : Ship within 1 day.

- Manufacturer Production time : 6-8 weeks (Normally have stocks)

- Weight : 0.001KG

Contact us to check the best price and real time inventory quantity for ADRF6602ACPZ-R7. If you need any more information about ADRF6602ACPZ-R7, you can also send us by email. Our email is [email protected], we will reply you in 12 hours.

- Rx mixer with integrated fractional-N PLL

- RF input frequency range: 1000 MHz to 3100 MHz

- Internal LO frequency range:

1550 MHz to 2150 MHz - Input P1dB: 14.8 dBm

- Input IP3: 30 dBm

- IIP3 optimization via external pin

- SSB noise figure:

IP3SET pin open: 13.8 dB

IP3SET pin at 3.3 V: 15 dB - Voltage conversion gain: 6.5 dB

- Matched 200 Ω IF output impedance

- IF 3 dB bandwidth: 500 MHz

- Programmable via 3-wire SPI interface

- 40-lead 6 mm × 6 mm LFCSP package

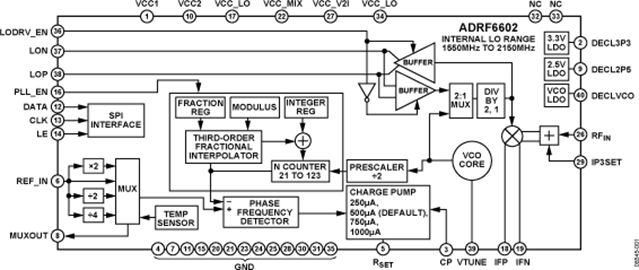

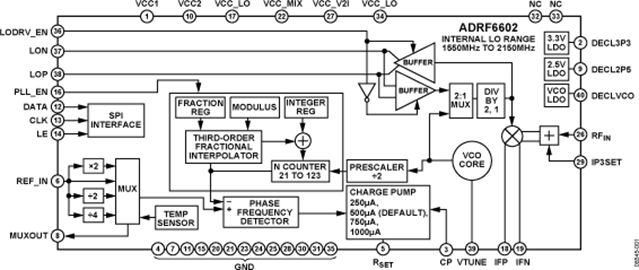

The ADRF6602 is a high dynamic range active mixer with integrated phase-locked loop (PLL) and voltage-controlled oscillator (VCO). The PLL/synthesizer uses a fractional-N PLL to generate an fLO input to the mixer. The reference input can be divided or multiplied and then applied to the PLL phase frequency detector (PFD).

The PLL can support input reference frequencies from 12 MHz to 160 MHz. The PFD output controls a charge pump whose output drives an off-chip loop filter.

The loop filter output is then applied to an integrated VCO. The VCO output at 2× fLO is applied to an LO divider, as well as to a programmable PLL divider. The programmable PLL divider is controlled by a Σ-Δ modulator (SDM). The modulus of the SDM can be programmed from 1 to 2047.

The active mixer converts the single-ended 50 Ω RF input to a 200 Ω differential IF output. The IF output can operate up to 500 MHz.

The ADRF6602 is fabricated using an advanced silicon-germanium BiCMOS process. It is available in a 40-lead, RoHS-compliant, 6 mm × 6 mm LFCSP with an exposed paddle. Performance is specified over the −40°C to +85°C temperature range.

Applications

- Cellular base stations

This designates products ADI does not recommend broadly for new designs.